엡솔의 R&D 로드맵

엡솔은 시장 규모와 기술의 발전 시점에 따라 체계적인 R&D 로드맵을 구축하고 있습니다. 현재 주력하고 있는 분야에서부터 미래 시장을 선도할 차세대 기술까지, 엡솔의 혁신적인 기술 발전 과정을 한눈에 확인하실 수 있습니다.

엡솔은 시장 규모와 기술의 발전 시점에 따라 체계적인 R&D 로드맵을 구축하고 있습니다. 현재 주력하고 있는 분야에서부터 미래 시장을 선도할 차세대 기술까지, 엡솔의 혁신적인 기술 발전 과정을 한눈에 확인하실 수 있습니다.

엡솔은 반도체 PKG의 고밀도, 고집적화, 소형화 추세에 맞춰 최적의 솔루션을 제공하며 시장을 선도하고 있습니다.

여러 칩을 겹쳐 쌓아 고밀도, 고집적 패키징을 가능하게 하는 기술을 확보했습니다.

부품의 크기와 두께를 최소화하는 기술을 확보했습니다.

전력 효율을 높이는 소재 기술을 개발했습니다.

신호의 손실을 최소화하여 데이터 전송 속도를 향상시키는 기술을 실현했습니다.

Through Silicon Via(TSV) 기술을 통해 넓은 대역폭을 구현하는 데 성공했습니다.

2014년을 기점으로 LOC / LLT와 Dicing Film 등 2D PKG 소재들을 개발해 왔습니다.

반도체 칩을 기판에 부착하는 데 사용되는 핵심 접착 소재입니다.

반도체 웨이퍼를 정밀하게 절단하는 데 사용되는 필름입니다.

쿼드 플랫 노-리드(QFN) 패키징 공정에 사용되는 테이프입니다.

반도체 칩을 기판에 부착하는 필름 소재입니다.

고밀도, 고집적화를 위한 TSV(Through Silicon Via) 기술에 사용되는 소재를 개발했습니다. 기존 기술에서 나아가 고성능을 위한 소재 개발을 목표로 했습니다.

TSV 공정 시 반도체 웨이퍼를 임시로 접착하는 소재입니다.

TSV 패키지 내부의 공간을 채우는 비전도성 필름입니다.

300도 이상의 고온에서도 안정성을 유지하는 소재입니다.

유연한 특성을 가진 차세대 메모리용 소재입니다.

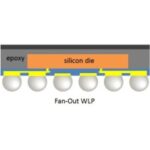

Fan-out Wafer Level Packaging에 사용되는 소재로, 패키징 효율을 높입니다.